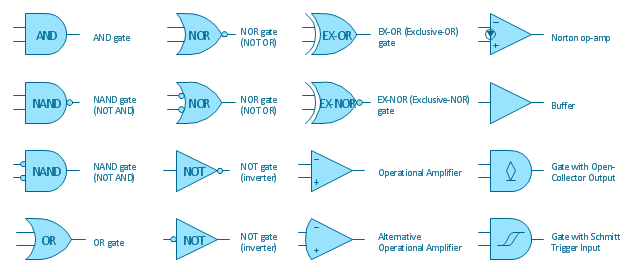

The vector stencils library "Logic gate diagram" contains 17 element symbols for drawing the logic gate diagrams.

"To build a functionally complete logic system, relays, valves (vacuum tubes), or transistors can be used. The simplest family of logic gates using bipolar transistors is called resistor-transistor logic (RTL). Unlike simple diode logic gates (which do not have a gain element), RTL gates can be cascaded indefinitely to produce more complex logic functions. RTL gates were used in early integrated circuits. For higher speed and better density, the resistors used in RTL were replaced by diodes resulting in diode-transistor logic (DTL). Transistor-transistor logic (TTL) then supplanted DTL. As integrated circuits became more complex, bipolar transistors were replaced with smaller field-effect transistors (MOSFETs); see PMOS and NMOS. To reduce power consumption still further, most contemporary chip implementations of digital systems now use CMOS logic. CMOS uses complementary (both n-channel and p-channel) MOSFET devices to achieve a high speed with low power dissipation." [Logic gate. Wikipedia]

The symbols example "Design elements - Logic gate diagram" was drawn using the ConceptDraw PRO diagramming and vector drawing software extended with the Electrical Engineering solution from the Engineering area of ConceptDraw Solution Park.

"To build a functionally complete logic system, relays, valves (vacuum tubes), or transistors can be used. The simplest family of logic gates using bipolar transistors is called resistor-transistor logic (RTL). Unlike simple diode logic gates (which do not have a gain element), RTL gates can be cascaded indefinitely to produce more complex logic functions. RTL gates were used in early integrated circuits. For higher speed and better density, the resistors used in RTL were replaced by diodes resulting in diode-transistor logic (DTL). Transistor-transistor logic (TTL) then supplanted DTL. As integrated circuits became more complex, bipolar transistors were replaced with smaller field-effect transistors (MOSFETs); see PMOS and NMOS. To reduce power consumption still further, most contemporary chip implementations of digital systems now use CMOS logic. CMOS uses complementary (both n-channel and p-channel) MOSFET devices to achieve a high speed with low power dissipation." [Logic gate. Wikipedia]

The symbols example "Design elements - Logic gate diagram" was drawn using the ConceptDraw PRO diagramming and vector drawing software extended with the Electrical Engineering solution from the Engineering area of ConceptDraw Solution Park.

HelpDesk

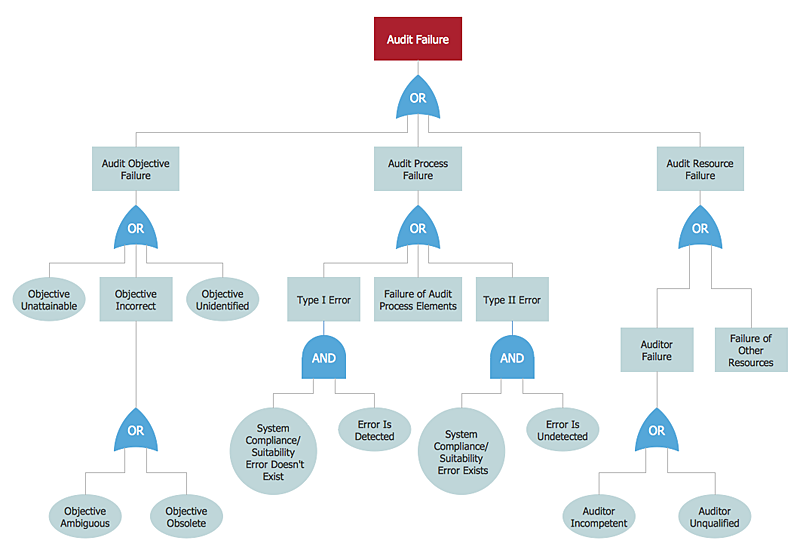

How to Create a Fault Tree Analysis Diagram (FTD) in ConceptDraw PRO

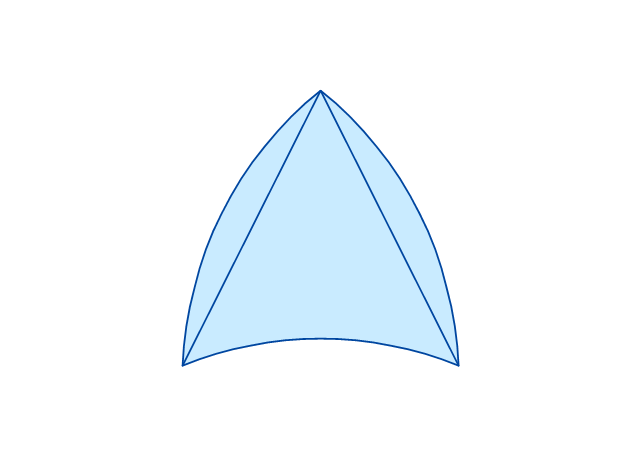

Fault Tree Diagram are logic diagram that shows the state of an entire system in a relationship of the conditions of its elements. Fault Tree Diagram are used to analyze the probability of functional system failures and safety accidents. ConceptDraw PRO allows you to create professional Fault Tree Diagrams using the basic FTD symbols. An FTD visualize a model of the processes within a system that can lead to the unlikely event. A fault tree diagrams are created using standard logic symbols . The basic elements in a fault tree diagram are gates and events.The vector stencils library "Fault tree analysis diagrams" contains 12 symbols for drawing FTA diagrams in the ConceptDraw PRO diagramming and vector drawing software extended with the Fault Tree Analysis Diagrams solution from the Engineering area of ConceptDraw Solution Park.

www.conceptdraw.com/ solution-park/ engineering-fault-tree-analysis-diagrams

www.conceptdraw.com/ solution-park/ engineering-fault-tree-analysis-diagrams

The vector stencils library "Fault tree analysis diagrams" contains 12 symbols for drawing Fault Tree Analysis (FTA) diagrams.

"Fault tree analysis (FTA) is a top down, deductive failure analysis in which an undesired state of a system is analyzed using Boolean logic to combine a series of lower-level events. This analysis method is mainly used in the fields of safety engineering and reliability engineering to understand how systems can fail, to identify the best ways to reduce risk or to determine (or get a feeling for) event rates of a safety accident or a particular system level (functional) failure. FTA is used in the aerospace, nuclear power, chemical and process, pharmaceutical, petrochemical and other high-hazard industries; but is also used in fields as diverse as risk factor identification relating to social service system failure.

In aerospace, the more general term "system Failure Condition" is used for the "undesired state" / Top event of the fault tree. These conditions are classified by the severity of their effects. The most severe conditions require the most extensive fault tree analysis. These "system Failure Conditions" and their classification are often previously determined in the functional Hazard analysis." [Fault tree analysis. Wikipedia]

The shapes example "Fault tree analysis diagrams" was created using the ConceptDraw PRO diagramming and vector drawing software extended with the Fault Tree Analysis Diagrams solution from the Engineering area of ConceptDraw Solution Park.

"Fault tree analysis (FTA) is a top down, deductive failure analysis in which an undesired state of a system is analyzed using Boolean logic to combine a series of lower-level events. This analysis method is mainly used in the fields of safety engineering and reliability engineering to understand how systems can fail, to identify the best ways to reduce risk or to determine (or get a feeling for) event rates of a safety accident or a particular system level (functional) failure. FTA is used in the aerospace, nuclear power, chemical and process, pharmaceutical, petrochemical and other high-hazard industries; but is also used in fields as diverse as risk factor identification relating to social service system failure.

In aerospace, the more general term "system Failure Condition" is used for the "undesired state" / Top event of the fault tree. These conditions are classified by the severity of their effects. The most severe conditions require the most extensive fault tree analysis. These "system Failure Conditions" and their classification are often previously determined in the functional Hazard analysis." [Fault tree analysis. Wikipedia]

The shapes example "Fault tree analysis diagrams" was created using the ConceptDraw PRO diagramming and vector drawing software extended with the Fault Tree Analysis Diagrams solution from the Engineering area of ConceptDraw Solution Park.

- Logic gate diagram - Template | Engineering | Electrical Drawing ...

- Drawing Of Logic Gate Symbol

- Draw The Traditional Symbols For And Or And Not Logic Gates

- Draw The Symbols Of And Gate

- Circuits and Logic Diagram Software | Electrical Symbols — Logic ...

- Circuits and Logic Diagram Software | Electrical Drawing Software ...

- Electrical Drawing Software and Electrical Symbols | Design ...

- Logic gate diagram

- Electrical Drawing Software and Electrical Symbols | Cross ...

- Design elements - Logic gate diagram | Electrical Drawing Software ...

- Electrical Drawing Software and Electrical Symbols | Circuits and ...

- Electrical Symbols , Electrical Diagram Symbols | Electrical Drawing ...

- Symbol Of And Gate In Technical Drawing

- Symbols Of Logic Gate

- Electrical Symbols — Logic Gate Diagram | Electrical Symbols ...

- Draw The Symbol For Or Gate

- Logic gate diagram - Template | Electrical Diagram | Electrical ...

- Draw The Symbol Of Or Gate

- Electrical Drawing Software and Electrical Symbols | How To use ...

- Gate Valve Symbol Drawings